Difference between revisions of "Talk:10359 DWT"

| (3 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| + | ==2008/12/09== | ||

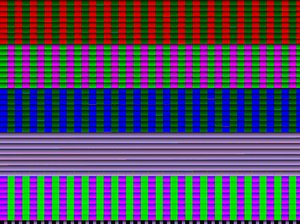

| + | 1. Tested with black line ends (tried white also) - this not deals with the problem I think - that false lines are in the beginning/middle of a frame line. After I added white ends to the channel 2 (write channel) - got a worse picture but false some of the false lines are on the same place - trying it in simulation. | ||

| + | {| border="1" cellpadding="2" | ||

| + | |- | ||

| + | | step 3 bad pic | ||

| + | |- | ||

| + | |[[Image:359_12092008_1700.jpeg|thumb]] | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | |||

| + | ==2008/12/08== | ||

| + | 1. Played with timing constraints but they seem to take no effect on the picture. There are line ends that I can make black and check on the picture - because that light blue lines on picture 2 don't depend on the test and short lines on the top of the 3rd picture don't depend also. | ||

| + | {| border="1" cellpadding="2" | ||

| + | |- | ||

| + | | step 1, direct|| step 2, 1st SDRAM vertical read || step 3, 2nd SDRAM horizontal read | ||

| + | |- | ||

| + | |[[Image:359_12082008_2030_1st.jpeg|thumb]] || [[Image:359_12082008_2030_2nd.jpeg|thumb]] || [[Image:359_12082008_2030_3rd.jpeg|thumb]] | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==2008/12/05== | ||

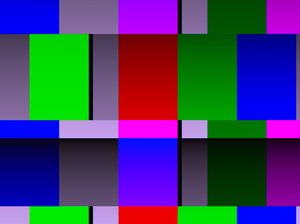

| + | 1. Got a little noise on the top of the frame due to bad timing - trying to apply proper constraints. | ||

| + | {| border="1" cellpadding="2" | ||

| + | |- | ||

| + | | step 1, direct|| step 2, 1st SDRAM vertical read || step 3, 2nd SDRAM horizontal read | ||

| + | |- | ||

| + | |[[Image:reference_img.jpeg|thumb]] || [[Image:359_120508_first_store.jpeg|thumb]] || [[Image:359_120508_second_store.jpeg|thumb]] | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==2008/11/18== | ||

| + | 1. Solved. Datapath is ok now. The mistake was in programming tile's x-sizes and shifts for a large frame (and in tests everithing was correct). | ||

| + | |||

==2008/11/13== | ==2008/11/13== | ||

1. Made datapath to/from memory for the tranform (added 2 channels) Currently get a set of 3 frames: | 1. Made datapath to/from memory for the tranform (added 2 channels) Currently get a set of 3 frames: | ||

Latest revision as of 11:32, 9 December 2008

Contents

[hide]2008/12/09

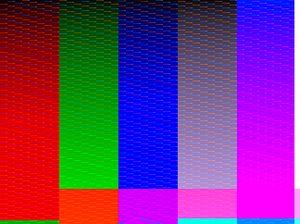

1. Tested with black line ends (tried white also) - this not deals with the problem I think - that false lines are in the beginning/middle of a frame line. After I added white ends to the channel 2 (write channel) - got a worse picture but false some of the false lines are on the same place - trying it in simulation.

| step 3 bad pic |

2008/12/08

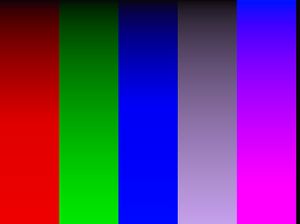

1. Played with timing constraints but they seem to take no effect on the picture. There are line ends that I can make black and check on the picture - because that light blue lines on picture 2 don't depend on the test and short lines on the top of the 3rd picture don't depend also.

| step 1, direct | step 2, 1st SDRAM vertical read | step 3, 2nd SDRAM horizontal read |

2008/12/05

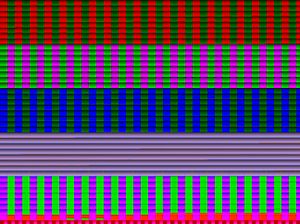

1. Got a little noise on the top of the frame due to bad timing - trying to apply proper constraints.

| step 1, direct | step 2, 1st SDRAM vertical read | step 3, 2nd SDRAM horizontal read |

2008/11/18

1. Solved. Datapath is ok now. The mistake was in programming tile's x-sizes and shifts for a large frame (and in tests everithing was correct).

2008/11/13

1. Made datapath to/from memory for the tranform (added 2 channels) Currently get a set of 3 frames:

step 1: frame from channel 1 goes directly to 353 and to the memory at the same time.

step 2: line by line frame is read from the memory and is written back to another location line by line: "read_line - write_line - read_line - write_line ..."

step 3: line by line frame is read from the memory.

| step 1, direct | step 2, 1st SDRAM read | step 3, 2nd SDRAM read |

Comments:

1. Feels like locations overlap somehow - this should be checked

2. No mistakes in the simulation stage (frames are 1620x4).

2008/07/31

Solved - 1. "right part is lost" - solved - mistake was in ch2_N_fp - line size in pixels

2. Made *.bit - board doesn't see sensors

2008/07/29

1. Simulation: output image is incorrect - right part is lost

2008/07/25

1. adjusted mcontr to read/write blocks to DDR

a. verified and corrected mistakes

TODO: adjust frame size more properly

2008/07/15

mcontr for block read/write is under work.

useful note:

1. SA[24:23]= Bank[1:0] 2. SA[22:10]= Row[12:0] 3. SA[9:0] = Col[9:0] 4. SA[12:8] - ...

2008/07/08

Basic 1D DWT for the whole frame is done. For each pixel in the Bayer Pattern should be calculated a separate DWT (because the difference can be significant?) - when I calculate mean value between neighbours (e.g., R & G) - the resulting picture is strange.