Trigger 393

Contents

[hide]Description

10389 board is required.

The triggering is used for one or several cameras synchronization or setting the frame rate (or fps). The conditions of the trigger can be generated either internally or externally. For external triggering a 4-conductor 2.5mm audio plug with cable (example: digikey) is required.

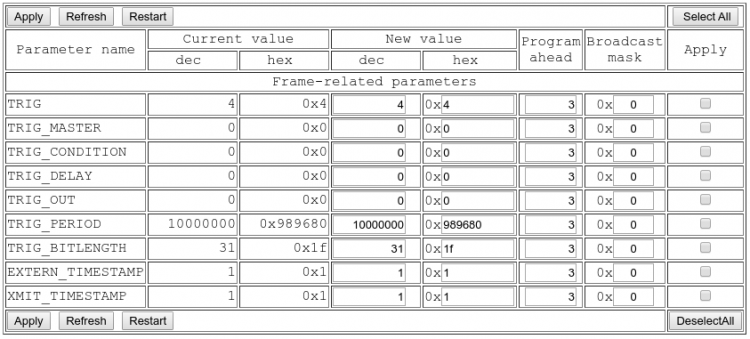

To program trigger go to: http://192.168.0.9/parsedit.php => External Trigger Controls

NOTE: Be careful with changing parameters when TRIG=4. Camera drivers are driven by the frame sync interrupts from the sensor, so if the sensor is not triggered - everything can get stuck. The Program Ahead value sets the number of frame sync interrupts the camera will wait wait for until a parameter is reprogrammed.

Parameters

| parameter | description |

| TRIG | Trigger mode. 0x0 - free running, 0x4 - triggered by external signal or FPGA timing generator, 0x14 - triggered in GRR mode |

| TRIG_MASTER | Master sensor_port (0..3) for triggering setup, other ports will have settings duplicated |

| TRIG_CONDITION | FPGA trigger sequencer trigger condition, 0 - internal, else dibits: 00 - do not use, 01 - keep, 10 - active low, 11 - active high for each GPIO[9:0] pin). 10389 board inverts signals, so 0x80000 - input from external connector, 0x08000 - input from internal flex cable (as in Eyesis) |

| TRIG_DELAY | FPGA trigger sequencer trigger delay, 32 bits in pixel clocks (100MHz or 10ns) |

| TRIG_OUT | FPGA trigger sequencer trigger output to GPIO, dibits: 00 - do not use, 01 - keep, 10 - active low GPIO output, 11 - active high GPIO output. 10389 board inverts signals, so 0x02000 - output to external connector (active high), 0x20000 - output to internal flex connector |

| TRIG_PERIOD | FPGA trigger sequencer output sync period (32 bits, in pixel clocks (100MHz or 10ns)). 0- stop. 1 - single, >=256 repetitive with specified period |

| TRIG_BITLENGTH | Bit length minus 1 (in pixel clock cycles) when transmitting/receiving timestamps, without timestamps the output pulse width is 8*(TRIG_BITLENGTH+1). Legal values 2..255 |

| EXTERN_TIMESTAMP | When 1 camera will use external timestamp (received over inter-camera synchronization cable) if it is available (no action when external syncronization is not connected), when 0 - local timestamp will be used |

| XMIT_TIMESTAMP | Specify output signal sent through internal/external connector (defined by TRIG_OUT). 0 - transmit just sync pulse (8*(TRIG_BITLENGTH+1) pixel clock periods long), 1 - pulse+timestamp 64*(TRIG_BITLENGTH+1) pixel clock periods long |

Examples

Internal periodic trigger (10 fps, from fpga generator)

- http://192.168.0.9/parsedit.php?sensor_port=0&immediate&TRIG_CONDITION=0&TRIG_PERIOD=10000000&TRIG=4

Internal periodic trigger (4 fps, from fpga generator) + output the signal to external port

External trigger receive

- http://192.168.0.9/parsedit.php?sensor_port=0&immediate&TRIG_CONDITION=0x95555&TRIG_OUT=0x66555&TRIG_PERIOD=100000000&TRIG=4

- at the same time the fpga generator will be generating a 1 fps signal

Manual triggering from PC

Enable

http://192.168.0.9:2323/trig/pointers

- TRIG=4 should be set in advance

- The command automatically sets a single-shot trigger mode with TRIG_PERIOD=0x1, but it writes the register directly into the FPGA,

not updating the TRIG_PERIOD in the PHP interface:

http://192.168.0.9/parsedit.php?TRIG&TRIG_CONDITION&TRIG_DELAY&TRIG_OUT&TRIG_PERIOD&TRIG_BITLENGTH&EXTERN_TIMESTAMP&XMIT_TIMESTAMP&refresh

Trigger/Refresh

http://192.168.0.9:8081/trig/pointers

Check status

http://192.168.0.9/parsedit.php?immediate&TRIG&TRIG_PERIOD&SENS_AVAIL&FRAME

Disable

- Update the TRIG_PERIOD in the PHP interface - or simply check the box and hit Apply:

http://192.168.0.9/parsedit.php?TRIG&TRIG_CONDITION&TRIG_DELAY&TRIG_OUT&TRIG_PERIOD&TRIG_BITLENGTH&EXTERN_TIMESTAMP&XMIT_TIMESTAMP&refresh

- Refresh until the changes are applied (with Program Ahead = 3 it's 3 times):

http://192.168.0.9:8081/trig/pointers

Links

- 10389 extension board