Difference between revisions of "10359 FPGA Simulation"

| (53 intermediate revisions by 2 users not shown) | |||

| Line 2: | Line 2: | ||

[[10359 work journal]]. | [[10359 work journal]]. | ||

| + | ==Summary== | ||

| + | 1. DDR test and phase adjust | ||

| + | |||

| + | 2. Switching channels | ||

| + | |||

| + | 3. Buffering one frame in DDR and switching between two channels (frame by frame, one buffered, one direct). | ||

| + | |||

| + | ==Working with 10359== | ||

| + | |||

| + | If any of the mentioned scripts is missing (currently it is 'switch_to_dcm1.php' and 'snapshot_mode_init.php') update CVS and copy it to camera. destination is: | ||

| + | ftp://192.168.0.9/usr/html/359 | ||

| + | |||

| + | ===Snapshot Mode=== | ||

| + | Currently works for 3 sensors | ||

| + | |||

| + | 1. Power on or reboot, then refresh (I'll use the default ip address of the camera) | ||

| + | http://192.168.0.9/ | ||

| + | , this will initialize the first sensor | ||

| + | |||

| + | 2. Initialize sensors and carefully adjust phases starting from channel 1: | ||

| + | http://192.168.0.9/359/sensors_init.php | ||

| + | Repeat for all channels: | ||

| + | Channel 1: | ||

| + | http://192.168.0.9/359/reg_write.php?adr=0x835&data=1 | ||

| + | adr - register address, 0x835 - "channel" register | ||

| + | |||

| + | http://192.168.0.9/359/phases_adjust.php?dcm=1&phase_shift=1&n=5 | ||

| + | dcm - number of DCM to use ('1','2','3' - same as channel numbers) | ||

| + | phase_shift - '1' - "+"-step, '2' - "-"-step | ||

| + | n - number of steps | ||

| + | |||

| + | if colors are inverted try | ||

| + | http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x6 | ||

| + | rst=1 - reset all DCMs | ||

| + | sphase[i]=1(default) - channel 'i' latches Vact/Hact on the FALLING edge of sclk0, sphase[i]=0 - RISING - KEEP SPHASE BITS FOR OTHER CHANNELS UNMODIFIED | ||

| + | (not helps - keep shifting the phase) | ||

| + | |||

| + | Channel 2: | ||

| + | http://192.168.0.9/359/reg_write.php?adr=0x835&data=2 | ||

| + | http://192.168.0.9/359/phases_adjust.php?dcm=2&phase_shift=1&n=5 | ||

| + | http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x5 - if colors are inverted | ||

| + | |||

| + | Channel 3: | ||

| + | http://192.168.0.9/359/reg_write.php?adr=0x835&data=4 | ||

| + | http://192.168.0.9/359/phases_adjust.php?dcm=3&phase_shift=1&n=5 | ||

| + | http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x3 - if colors are inverted | ||

| + | |||

| + | 3. Put the first sensor in the Snapshot Mode: | ||

| + | http://192.168.0.9/ccam.php?trig=async&mode=set | ||

| + | |||

| + | 4. Reinitialize everything (look up in source, also some kind of log will be on that page) | ||

| + | http://192.168.0.9/359/tests_for_96mhz.php | ||

| + | Procedures: | ||

| + | |||

| + | - set delay between trigger signals to sensors (1 step is 96MHz period). Default is 0. | ||

| + | |||

| + | - initialize other sensors (Parameters from sensor 1 are taken) | ||

| + | |||

| + | - send initialization sequence to DDR | ||

| + | |||

| + | - proper channel is selected (0x10001, in fact it is mode) | ||

| + | |||

| + | 0x10XXX (XXX is 001,010,100) - for switching frames from sensors on the output. One direct, one buffered. | ||

| + | |||

| + | 0x00XXX - frames from one channel (depends on XXX) go directly to the output | ||

| + | |||

| + | - set frame resolution | ||

| + | |||

| + | - initialize memory controller channels | ||

| + | |||

| + | 5. Start the compressor and get a couple of frames | ||

| + | http://192.168.0.9/compressor.php?cmd=run | ||

| + | http://192.168.0.9/sync.php?role=self&fps=single | ||

| + | for another couple refresh the second link. | ||

| + | |||

| + | 6. The frames will be written to the [[circbuf]] | ||

| + | http://192.168.0.9:8081/pointers/ - will show some useful info | ||

| + | http://192.168.0.9:8081/torp/next/img/save - surf the circbuf | ||

| + | http://192.168.0.9:8081/torp/prev/img/save - surf the circbuf | ||

| + | |||

| + | 7. To stop the compressor | ||

| + | http://192.168.0.9/compressor.php?cmd=run | ||

| + | http://192.168.0.9/sync.php?role=self&fps=single | ||

| + | It stops after it gets the next piece of data - that will be two frames in this case. | ||

| + | |||

| + | ===Some other scripts and modes=== | ||

| + | 1. after power is on, go to (I'll use the default ip address of the camera) | ||

| + | http://192.168.0.9/camvc.html | ||

| + | , this will initialize the first sensor | ||

| + | |||

| + | 2. to initialize the other 2 sensors use | ||

| + | http://192.168.0.9/359/sensors_init.php | ||

| + | |||

| + | 3. this will help you to switch to channel 1 | ||

| + | channel[5]- mode (should be 1 for direct data path), | ||

| + | channel[2]- switch to sensor 3, | ||

| + | channel[1]- switch to sensor 2, | ||

| + | channel[0]- switch to sensor 1): | ||

| + | |||

| + | http://192.168.0.9/359/reg_write.php?adr=0x835&data=1 | ||

| + | |||

| + | 4. to test the DDR memory | ||

| + | http://192.168.0.9/359/mem_test.php?row_adr=0x006&N=5 | ||

| + | - parameters are start address and the number of rows to write and read | ||

| + | |||

| + | 5.if you need to change phase of the clock to any sensor | ||

| + | http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=7&dcm=1&phase_shift=1&n=5 | ||

| + | rst - reset all DCMs | ||

| + | sphase[i]=1 - channel 'i' latches Vact/Hact on the FALLING edge of sclk0, sphase[i]=0 - RISING | ||

| + | dcm - number of DCM to use ('1','2','3' - same as channel numbers) | ||

| + | phase_shift - '1' - "+"-step, '0' - "-"-step | ||

| + | n - number of steps | ||

| + | |||

| + | 6. to set frame size and some other things | ||

| + | http://192.168.0.9/359/tests_for_96mhz.php?phase_shift=0&delay=0x000fffff&channel=33&pixes=2595&lines=1940 | ||

| + | One of that things is memory controller initialization, registers are described in | ||

| + | /elphel353-7.1/os/linux-2.6-tag--devboard-R2_10-4/arch/cris/arch-v32/drivers/elphel/x353.h | ||

| + | |||

| + | ==2008/10/31== | ||

| + | 1. Was able to store the whole frame in SDRAM with modified controller. | ||

| + | |||

| + | 2. Not to forget - "ccam.php?trig=async&mode=set" works after calling the camera interface (camvc.html) | ||

| + | |||

| + | --[[User:Oleg|Oleg]] 07:22, 31 October 2008 (CDT) | ||

| + | |||

| + | ==2008/10/01== | ||

| + | 1. after reconfiguration (running camera_demo twice) the image gets darker even with 353+sensor | ||

| + | |||

| + | --[[User:Oleg|Oleg]] 17:40, 30 September 2008 (CDT) | ||

| + | |||

| + | ==2008/09/30== | ||

| + | update2: | ||

| + | |||

| + | 1. different md5s - in camera_demo [RSCALE]=305, and the one from *.conf [RSCALE] => 303 - that made the difference. - with [RSCALE]=303 md5 is correct. | ||

| + | |||

| + | --[[User:Oleg|Oleg]] 17:39, 30 September 2008 (CDT) | ||

| + | |||

| + | update1: | ||

| + | |||

| + | 1. images from sensors are the same! reconnection of one of the cables fixed that - md5=4ebe69ad27d260c27d667747c431dc96 | ||

| + | |||

| + | 2. different md5s is the result of the different configuration. Running adapted camera_demo with 353+sensor gave md5=4ebe69ad27d260c27d667747c431dc96. | ||

| + | |||

| + | so again ... I just need to find out what is wrong with scripts - why color gain is programmed incorrectly? But it should. And - gain doesn't change after it is reprogrammed while sensor is working. | ||

| + | |||

| + | Images look very similar | ||

| + | {| border="1" cellpadding="2" | ||

| + | |- | ||

| + | | reference || channel 1 || channel 2 | ||

| + | |- | ||

| + | | md5=ab97b19d132a5491386895c5d460f87c || md5=131fa048a5396de57cc9e075b7282c41 || md5=4ebe69ad27d260c27d667747c431dc96 | ||

| + | |- | ||

| + | |[[Image:reference_img.jpeg|thumb]] || [[Image:359_ch1_img.jpeg|thumb]] || [[Image:359_ch2_img.jpeg|thumb]] | ||

| + | |||

| + | |- | ||

| + | |} | ||

| + | ==2008/09/29== | ||

| + | 1. Images are stable now | ||

| + | 2. md5 is different - the pattern image from sensor+359 is darker than from just the sensor. | ||

| + | MD5 = 60119f4aea02d4624aad045221b4ede0 | ||

| + | |||

| + | ==2008/09/19== | ||

| + | ==="353+359+2 sensors in ch0 and ch1"=== | ||

| + | ====a)==== | ||

| + | x359.bit: | ||

| + | * data from channel 0 after resync-ing to internal sclk0 goes to output which is synchronous to pclk at 353. Clock tree: | ||

| + | 353 -> pclk-> 359's DCM -> sclk0 | ||

| + | * other functionality is cut | ||

| + | * experimented with different cables and, sensors | ||

| + | |||

| + | I get good images, sometimes not - looks like depends on the boot. This happens after the power off and the cable from 359 to 353 is a bit deformed, then power on. | ||

| + | |||

| + | Images do not change if the cable is deformed during camera work. | ||

| + | |||

| + | Bad images are unstable and can be of different color, the test pattern is broken, but stable. | ||

| + | |||

| + | |||

| + | |||

| + | Conclusion: | ||

| + | Misconfiguration? | ||

| + | |||

| + | {| border="1" cellpadding="2" | ||

| + | |- | ||

| + | | Good || Bad | ||

| + | |- | ||

| + | |[[Image:Good1.jpeg|thumb]]|| [[Image:Bad1.jpeg|thumb]] | ||

| + | |- | ||

| + | | || [[Image:Bad2.jpeg|thumb]] | ||

| + | |- | ||

| + | | Test patterns || || Etalon (353+sensor) | ||

| + | |- | ||

| + | |[[Image:Good2.jpeg|thumb]] || [[Image:Bad3.jpeg|thumb]] || [[Image:Etalon.jpeg|thumb]] | ||

| + | |||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ====b)==== | ||

| + | x359.bit: | ||

| + | * data from channels 0 and 1 after resync-ing to internal sclk0 is multiplexed to output which is synchronous to pclk at 353. Clock tree: | ||

| + | 353 -> pclk-> 359's DCM -> sclk0 | ||

| + | * other functionality is cut | ||

| + | * experimented with different cables and, sensors | ||

| + | |||

| + | All images are broken. | ||

| + | |||

| + | ==2008/06/09== | ||

| + | 1. 1 direct + 2 buffered images - done (added 5th cnannel to mcontr - simulated and tested as well). Trying to get difference between frames. | ||

| + | |||

| + | ==2008/04/25== | ||

| + | 1. make so that it will take less steps to get the frame from the sensor. | ||

| + | |||

| + | ==2008/04/22== | ||

| + | 1. Wrote a script for initializing all the sensors (they needed to set image frame size to 2596x1940 for the compressor to work properly) - sensors_init.php. It just copies parameters from sensor | ||

| + | |||

| + | 2. Buffering one frame in DDR and switching between two channels (frame by frame, one buffered, one direct). But this needs to be tested more properly because there's a two black pixel line on the left side - that means Hact is latched two tacts earlier than data. | ||

| + | |||

| + | ==2008/04/13== | ||

| + | 1. ch1 - written/read from DDR, ch2 - just comes through. | ||

| + | |||

| + | Simulator output: ch2...ch1-ch2-ch1-ch2 | ||

| + | |||

| + | Board output : i can see images changing, but when the compressor is turned on - ch1-ch1-ch1... Does the compressor drop frames (i tried to add a delay (still experimenting))? | ||

| + | |||

| + | ==2008/04/09== | ||

| + | 1. "Somehow the last row address I can reach is 0x7ff. Trying simulation". | ||

| + | |||

| + | It's ok now - I was uncarefully modified 'descrproc' module. | ||

| + | |||

| + | 2. Test frame is in DDR. | ||

| + | |||

| + | ==2008/04/08== | ||

| + | 1. Somehow the last row address I can reach is 0x7ff. Trying simulation. | ||

| + | |||

| + | ==2008/04/05== | ||

| + | 1. With a couple of counters removed the memory test eventually ran fine @96MHz (again with bit0 missing). Need to put constraints to that path. | ||

| + | |||

| + | ==2008/04/04== | ||

| + | 1. Vact&Hact based on counters - test counter work - do not work | ||

| + | |||

| + | 2. Make a memory test, through channel 3 have the ability to read all the DDR - Done, bit0 is not changing. Here's an example (other bits were checked @48MHz and they are ok). | ||

| + | Write DDR | ||

| + | Sent array to Row 0x00000003 | ||

| + | 00030000 00030001 00030002 00030003 | ||

| + | 00030010 00030011 00030012 00030013 | ||

| + | 00030020 00030021 00030022 00030023 | ||

| + | 00030030 00030031 00030032 00030033 | ||

| + | |||

| + | Read DDR | ||

| + | Acquired data from row 0x00000003 | ||

| + | 00020000 00020000 00020002 00020002 | ||

| + | 00020010 00020010 00020012 00020012 | ||

| + | 00020020 00020020 00020022 00020022 | ||

| + | 00020030 00020030 00020032 00020032 | ||

| + | |||

| + | 3. Run a little (for 1 page) memory test @96MHz. This is before phase shift adjust... | ||

| + | Write DDR | ||

| + | Sent array to Row 0x00000003 | ||

| + | 00030000 00030001 00030002 00030003 00030004 00030005 00030006 00030007 00030008 00030009 0003000a 0003000b 0003000c 0003000d 0003000e 0003000f | ||

| + | 00030010 00030011 00030012 00030013 00030014 00030015 00030016 00030017 00030018 00030019 0003001a 0003001b 0003001c 0003001d 0003001e 0003001f | ||

| + | 00030020 00030021 00030022 00030023 00030024 00030025 00030026 00030027 00030028 00030029 0003002a 0003002b 0003002c 0003002d 0003002e 0003002f | ||

| + | 00030030 00030031 00030032 00030033 00030034 00030035 00030036 00030037 00030038 00030039 0003003a 0003003b 0003003c 0003003d 0003003e 0003003f | ||

| + | 00030040 00030041 00030042 00030043 00030044 00030045 00030046 00030047 00030048 00030049 0003004a 0003004b 0003004c 0003004d 0003004e 0003004f | ||

| + | 00030050 00030051 00030052 00030053 00030054 00030055 00030056 00030057 00030058 00030059 0003005a 0003005b 0003005c 0003005d 0003005e 0003005f | ||

| + | 00030060 00030061 00030062 00030063 00030064 00030065 00030066 00030067 00030068 00030069 0003006a 0003006b 0003006c 0003006d 0003006e 0003006f | ||

| + | 00030070 00030071 00030072 00030073 00030074 00030075 00030076 00030077 00030078 00030079 0003007a 0003007b 0003007c 0003007d 0003007e 0003007f | ||

| + | 00030080 00030081 00030082 00030083 00030084 00030085 00030086 00030087 00030088 00030089 0003008a 0003008b 0003008c 0003008d 0003008e 0003008f | ||

| + | 00030090 00030091 00030092 00030093 00030094 00030095 00030096 00030097 00030098 00030099 0003009a 0003009b 0003009c 0003009d 0003009e 0003009f | ||

| + | 000300a0 000300a1 000300a2 000300a3 000300a4 000300a5 000300a6 000300a7 000300a8 000300a9 000300aa 000300ab 000300ac 000300ad 000300ae 000300af | ||

| + | 000300b0 000300b1 000300b2 000300b3 000300b4 000300b5 000300b6 000300b7 000300b8 000300b9 000300ba 000300bb 000300bc 000300bd 000300be 000300bf | ||

| + | 000300c0 000300c1 000300c2 000300c3 000300c4 000300c5 000300c6 000300c7 000300c8 000300c9 000300ca 000300cb 000300cc 000300cd 000300ce 000300cf | ||

| + | 000300d0 000300d1 000300d2 000300d3 000300d4 000300d5 000300d6 000300d7 000300d8 000300d9 000300da 000300db 000300dc 000300dd 000300de 000300df | ||

| + | 000300e0 000300e1 000300e2 000300e3 000300e4 000300e5 000300e6 000300e7 000300e8 000300e9 000300ea 000300eb 000300ec 000300ed 000300ee 000300ef | ||

| + | 000300f0 000300f1 000300f2 000300f3 000300f4 000300f5 000300f6 000300f7 000300f8 000300f9 000300fa 000300fb 000300fc 000300fd 000300fe 000300ff | ||

| + | 00030100 00030101 00030102 00030103 00030104 00030105 00030106 00030107 00030108 00030109 0003010a 0003010b 0003010c 0003010d 0003010e 0003010f | ||

| + | 00030110 00030111 00030112 00030113 00030114 00030115 00030116 00030117 00030118 00030119 0003011a 0003011b 0003011c 0003011d 0003011e 0003011f | ||

| + | 00030120 00030121 00030122 00030123 00030124 00030125 00030126 00030127 00030128 00030129 0003012a 0003012b 0003012c 0003012d 0003012e 0003012f | ||

| + | 00030130 00030131 00030132 00030133 00030134 00030135 00030136 00030137 00030138 00030139 0003013a 0003013b 0003013c 0003013d 0003013e 0003013f | ||

| + | 00030140 00030141 00030142 00030143 00030144 00030145 00030146 00030147 00030148 00030149 0003014a 0003014b 0003014c 0003014d 0003014e 0003014f | ||

| + | 00030150 00030151 00030152 00030153 00030154 00030155 00030156 00030157 00030158 00030159 0003015a 0003015b 0003015c 0003015d 0003015e 0003015f | ||

| + | 00030160 00030161 00030162 00030163 00030164 00030165 00030166 00030167 00030168 00030169 0003016a 0003016b 0003016c 0003016d 0003016e 0003016f | ||

| + | 00030170 00030171 00030172 00030173 00030174 00030175 00030176 00030177 00030178 00030179 0003017a 0003017b 0003017c 0003017d 0003017e 0003017f | ||

| + | 00030180 00030181 00030182 00030183 00030184 00030185 00030186 00030187 00030188 00030189 0003018a 0003018b 0003018c 0003018d 0003018e 0003018f | ||

| + | 00030190 00030191 00030192 00030193 00030194 00030195 00030196 00030197 00030198 00030199 0003019a 0003019b 0003019c 0003019d 0003019e 0003019f | ||

| + | 000301a0 000301a1 000301a2 000301a3 000301a4 000301a5 000301a6 000301a7 000301a8 000301a9 000301aa 000301ab 000301ac 000301ad 000301ae 000301af | ||

| + | 000301b0 000301b1 000301b2 000301b3 000301b4 000301b5 000301b6 000301b7 000301b8 000301b9 000301ba 000301bb 000301bc 000301bd 000301be 000301bf | ||

| + | 000301c0 000301c1 000301c2 000301c3 000301c4 000301c5 000301c6 000301c7 000301c8 000301c9 000301ca 000301cb 000301cc 000301cd 000301ce 000301cf | ||

| + | 000301d0 000301d1 000301d2 000301d3 000301d4 000301d5 000301d6 000301d7 000301d8 000301d9 000301da 000301db 000301dc 000301dd 000301de 000301df | ||

| + | 000301e0 000301e1 000301e2 000301e3 000301e4 000301e5 000301e6 000301e7 000301e8 000301e9 000301ea 000301eb 000301ec 000301ed 000301ee 000301ef | ||

| + | 000301f0 000301f1 000301f2 000301f3 000301f4 000301f5 000301f6 000301f7 000301f8 000301f9 000301fa 000301fb 000301fc 000301fd 000301fe 000301ff | ||

| + | |||

| + | Read DDR | ||

| + | Acquired data from Row 0x00000003 | ||

| + | 00020000 00020000 00020002 00020002 00020004 00020008 0002000a 0002000a 0002000c 0002000e 00020010 00020010 00020012 00020012 00020014 00020014 | ||

| + | 00020016 00020018 0002001a 0002001a 0002001c 0002001c 0002001e 0002001e 00020020 00020020 00020022 00020022 00020024 00000000 00000000 00020024 | ||

| + | 00020026 00020026 00020028 00020028 0002002a 00020050 00020052 00020054 00020056 0002004a 0002004c 00020056 00020058 00020052 00020054 00020058 | ||

| + | 0002005a 0002005a 0002005c 0002005c 0002005e 0002005e 00020060 00020070 00020072 00020072 00020074 00020074 00020076 0002006e 00020070 00020076 | ||

| + | 00020078 0002007a 0002007c 0002007c 0002007e 00020088 0002008a 00020080 00020082 00020082 00020084 00020084 00020086 0002008a 0002008c 0002008c | ||

| + | 0002008e 0002008e 00020090 00020090 00020092 00000000 00000000 000200a0 000200a2 000200a4 000200a6 000200a6 000200a8 0002009e 000200a0 000200a8 | ||

| + | 000200aa 000200ae 000200b0 000200b0 000200b2 00000000 00000000 000200b2 000200b4 000200b8 000200ba 000200ba 000200bc 00000000 00000000 000200bc | ||

| + | 000200be 000200c0 000200c2 000200c2 000200c4 000200c4 000200c6 000200c6 000200c8 000200ca 000200cc 000200cc 000200ce 000200ce 000200d0 000200d0 | ||

| + | 000200d2 000200d2 000200d4 000200d4 000200d6 000200d6 000200d8 000200d8 000200da 000200dc 000200de 000200de 000200e0 000200e0 000200e2 000200e2 | ||

| + | 000200e4 000200e4 000200e6 000200e6 000200e8 00000000 00000000 000200e8 000200ea 000200ee 000200f0 000200f0 000200f2 000200f2 000200f4 000200f4 | ||

| + | 000200f6 00020100 00020102 00020102 00020104 00000000 00000000 00020104 00020106 00020108 0002010a 0002010a 0002010c 00000000 00000000 0002010c | ||

| + | 0002010e 0002010e 00020110 00020110 00020112 00020138 0002013a 0002013a 0002013c 00020142 00020144 00020144 00020146 00020136 00020138 00020146 | ||

| + | 00020148 00020148 0002014a 0002014a 0002014c 0002014c 0002014e 0002014e 00020150 00020152 00020154 00020154 00020156 00020156 00020158 00020158 | ||

| + | 0002015a 0002015c 0002015e 0002015e 00020160 00020160 00020162 00020162 00020164 00000000 00000000 00020164 00020166 00020166 00020168 00020168 | ||

| + | 0002016a 0002016a 0002016c 0002016c 0002016e 0002016e 00020170 00020172 00020174 00020176 00020178 00020178 0002017a 0002017a 0002017c 0002017c | ||

| + | 0002017e 00000000 00000000 0002017e 00020180 00000000 00000000 00020180 00020182 00020182 00020184 00020184 00020186 00020186 00020188 00020188 | ||

| + | 0002018a 00000000 00000000 0002018a 0002018c 0002018e 00020190 00020190 00020192 00020194 00020196 00020196 00020198 00000000 00000000 00020198 | ||

| + | 0002019a 000201a0 000201a2 000201a2 000201a4 000201c4 000201c6 000201ce 000201d0 000201d0 000201d2 000201d2 000201d4 000201cc 000201ce 000201d4 | ||

| + | 000201d6 000201d6 000201d8 000201d8 000201da 000201da 000201dc 00000000 00000000 00000000 00000000 00000000 00000000 000201dc 000201de 000201de | ||

| + | 000201e0 000201e0 000201e2 000201e2 000201e4 000201fa 000201fc 000201fc 000201fe 000201fe 000201f6 000201f6 000201f8 000201f8 000201fa 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 | ||

| + | |||

| + | ==2008/03/25== | ||

| + | 1. It's not 10359A yet. | ||

| + | 2. There are problems with storing the whole image in the DDR and reading it back. Sync signals were lost. The simulation is ok, but there are too small images. It could be: | ||

| + | a. Incorrect address range written to mcontr registers?! | ||

| + | - save the last row address (for 1620x1200, it's near to (2^21)/(2^10 - number of columns in a row)= 2^11 = 0x8000; | ||

| + | b. ... | ||

| + | |||

| + | ==2008/03/20== | ||

| + | 1. @96MHz, data from sensor replaced by 8 bit counter - there are vertical lines - that means one of the bits is late. Add a phase adjust to the 1st DCM. | ||

| + | |||

| + | 2. Apply low drive strength to all the pins interface 353. | ||

| + | This removed vertical lines from section 1. | ||

| + | |||

| + | 3. DDR | ||

| + | MaxFrame = (2592x1936)x16 ~ (2^12 x 2^11)x16 = (2^23)x16 = 8M16 = 1 bank of MT46V32M16BN-5B | ||

| + | |||

| + | ==2008/03/19== | ||

| + | 1. Initialize/Write/Read DDR @96MHz | ||

| + | It's ok. | ||

| + | |||

| + | ==2008/03/18== | ||

| + | 1. make i2c work @96MHz | ||

| + | There's a suspicion it works unstable, so TODO is: | ||

| + | a. read an internal counter | ||

| + | b. write/read BRAM - done | ||

| + | |||

| + | All's fine. Next Step - Initialize/Write/Read DDR @96MHz. This was unstable because of the need to adjust phase. | ||

| + | |||

| + | 2. make the image look like as if data doesn't go through DDR. There're small differences. | ||

| + | All's good | ||

| + | Reg Address: 0x0835 | ||

| + | Data: | ||

| + | bits[4:0]=00001 - channel1 -> DDR -> 359 -> 353 | ||

| + | bits[4:0]=00010 - channel2 -> DDR -> 359 -> 353 | ||

| + | bits[4:0]=00100 - channel3 -> DDR -> 359 -> 353 | ||

| + | bits[4:0]=01001 - counter (accompanied with syncs from sensor1) -> DDR -> 359 -> 353 | ||

| + | bits[4]=1 - counter (accompanied with syncs from sensor1) -> 353 | ||

| + | |||

| + | |||

| + | ==2008/03/17== | ||

| + | 1. Put all FFs to negedge.And verify it. - done | ||

| + | |||

| + | 2. Make i2c channels switching work fine - it's ok? but -> | ||

| + | |||

| + | 3. i2c first work @96MHz | ||

| + | |||

==2008/03/13== | ==2008/03/13== | ||

TODO: | TODO: | ||

| + | |||

1. Mistakes during reads?! Check read and write addresses. | 1. Mistakes during reads?! Check read and write addresses. | ||

| + | |||

| + | !!!! FORGOT TO INITIALIZE CHANNEL 2 !!!! | ||

| + | |||

| + | This chain works fine now: | ||

| + | "sensor -> channel's 0 buffer -> DDR -> channel's 2 line buffer -> to 353" | ||

| + | |||

==2008/03/12== | ==2008/03/12== | ||

1. DDR channel 3 has no problems @48MHz | 1. DDR channel 3 has no problems @48MHz | ||

Latest revision as of 05:22, 31 October 2008

The main page for the board is 10359.

Contents

[hide]- 1 Summary

- 2 Working with 10359

- 3 2008/10/31

- 4 2008/10/01

- 5 2008/09/30

- 6 2008/09/29

- 7 2008/09/19

- 8 2008/06/09

- 9 2008/04/25

- 10 2008/04/22

- 11 2008/04/13

- 12 2008/04/09

- 13 2008/04/08

- 14 2008/04/05

- 15 2008/04/04

- 16 2008/03/25

- 17 2008/03/20

- 18 2008/03/19

- 19 2008/03/18

- 20 2008/03/17

- 21 2008/03/13

- 22 2008/03/12

- 23 2008/02/20

- 24 2008/02/20. Understanding how 353's mcontr works

- 25 2008/02/14

Summary

1. DDR test and phase adjust

2. Switching channels

3. Buffering one frame in DDR and switching between two channels (frame by frame, one buffered, one direct).

Working with 10359

If any of the mentioned scripts is missing (currently it is 'switch_to_dcm1.php' and 'snapshot_mode_init.php') update CVS and copy it to camera. destination is:

ftp://192.168.0.9/usr/html/359

Snapshot Mode

Currently works for 3 sensors

1. Power on or reboot, then refresh (I'll use the default ip address of the camera)

http://192.168.0.9/

, this will initialize the first sensor

2. Initialize sensors and carefully adjust phases starting from channel 1:

http://192.168.0.9/359/sensors_init.php Repeat for all channels: Channel 1: http://192.168.0.9/359/reg_write.php?adr=0x835&data=1 adr - register address, 0x835 - "channel" register http://192.168.0.9/359/phases_adjust.php?dcm=1&phase_shift=1&n=5 dcm - number of DCM to use ('1','2','3' - same as channel numbers) phase_shift - '1' - "+"-step, '2' - "-"-step n - number of steps if colors are inverted try http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x6 rst=1 - reset all DCMs sphase[i]=1(default) - channel 'i' latches Vact/Hact on the FALLING edge of sclk0, sphase[i]=0 - RISING - KEEP SPHASE BITS FOR OTHER CHANNELS UNMODIFIED (not helps - keep shifting the phase) Channel 2: http://192.168.0.9/359/reg_write.php?adr=0x835&data=2 http://192.168.0.9/359/phases_adjust.php?dcm=2&phase_shift=1&n=5 http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x5 - if colors are inverted Channel 3: http://192.168.0.9/359/reg_write.php?adr=0x835&data=4 http://192.168.0.9/359/phases_adjust.php?dcm=3&phase_shift=1&n=5 http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=0x3 - if colors are inverted

3. Put the first sensor in the Snapshot Mode:

http://192.168.0.9/ccam.php?trig=async&mode=set

4. Reinitialize everything (look up in source, also some kind of log will be on that page)

http://192.168.0.9/359/tests_for_96mhz.php

Procedures:

- set delay between trigger signals to sensors (1 step is 96MHz period). Default is 0.

- initialize other sensors (Parameters from sensor 1 are taken)

- send initialization sequence to DDR

- proper channel is selected (0x10001, in fact it is mode)

0x10XXX (XXX is 001,010,100) - for switching frames from sensors on the output. One direct, one buffered.

0x00XXX - frames from one channel (depends on XXX) go directly to the output

- set frame resolution

- initialize memory controller channels

5. Start the compressor and get a couple of frames

http://192.168.0.9/compressor.php?cmd=run http://192.168.0.9/sync.php?role=self&fps=single

for another couple refresh the second link.

6. The frames will be written to the circbuf

http://192.168.0.9:8081/pointers/ - will show some useful info http://192.168.0.9:8081/torp/next/img/save - surf the circbuf http://192.168.0.9:8081/torp/prev/img/save - surf the circbuf

7. To stop the compressor

http://192.168.0.9/compressor.php?cmd=run http://192.168.0.9/sync.php?role=self&fps=single

It stops after it gets the next piece of data - that will be two frames in this case.

Some other scripts and modes

1. after power is on, go to (I'll use the default ip address of the camera)

http://192.168.0.9/camvc.html

, this will initialize the first sensor

2. to initialize the other 2 sensors use

http://192.168.0.9/359/sensors_init.php

3. this will help you to switch to channel 1 channel[5]- mode (should be 1 for direct data path), channel[2]- switch to sensor 3, channel[1]- switch to sensor 2, channel[0]- switch to sensor 1):

http://192.168.0.9/359/reg_write.php?adr=0x835&data=1

4. to test the DDR memory

http://192.168.0.9/359/mem_test.php?row_adr=0x006&N=5

- parameters are start address and the number of rows to write and read

5.if you need to change phase of the clock to any sensor

http://192.168.0.9/359/phases_adjust.php?rst=0&sphase=7&dcm=1&phase_shift=1&n=5 rst - reset all DCMs sphase[i]=1 - channel 'i' latches Vact/Hact on the FALLING edge of sclk0, sphase[i]=0 - RISING dcm - number of DCM to use ('1','2','3' - same as channel numbers) phase_shift - '1' - "+"-step, '0' - "-"-step n - number of steps

6. to set frame size and some other things

http://192.168.0.9/359/tests_for_96mhz.php?phase_shift=0&delay=0x000fffff&channel=33&pixes=2595&lines=1940

One of that things is memory controller initialization, registers are described in

/elphel353-7.1/os/linux-2.6-tag--devboard-R2_10-4/arch/cris/arch-v32/drivers/elphel/x353.h

2008/10/31

1. Was able to store the whole frame in SDRAM with modified controller.

2. Not to forget - "ccam.php?trig=async&mode=set" works after calling the camera interface (camvc.html)

--Oleg 07:22, 31 October 2008 (CDT)

2008/10/01

1. after reconfiguration (running camera_demo twice) the image gets darker even with 353+sensor

--Oleg 17:40, 30 September 2008 (CDT)

2008/09/30

update2:

1. different md5s - in camera_demo [RSCALE]=305, and the one from *.conf [RSCALE] => 303 - that made the difference. - with [RSCALE]=303 md5 is correct.

--Oleg 17:39, 30 September 2008 (CDT)

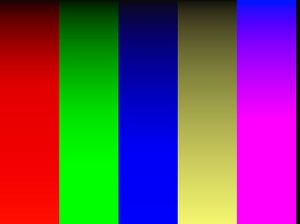

update1:

1. images from sensors are the same! reconnection of one of the cables fixed that - md5=4ebe69ad27d260c27d667747c431dc96

2. different md5s is the result of the different configuration. Running adapted camera_demo with 353+sensor gave md5=4ebe69ad27d260c27d667747c431dc96.

so again ... I just need to find out what is wrong with scripts - why color gain is programmed incorrectly? But it should. And - gain doesn't change after it is reprogrammed while sensor is working.

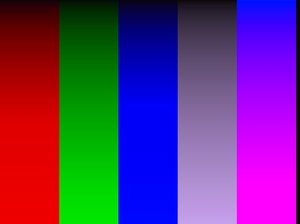

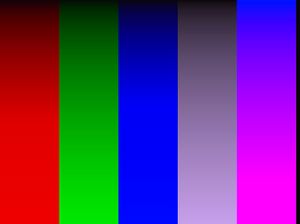

Images look very similar

| reference | channel 1 | channel 2 |

| md5=ab97b19d132a5491386895c5d460f87c | md5=131fa048a5396de57cc9e075b7282c41 | md5=4ebe69ad27d260c27d667747c431dc96 |

2008/09/29

1. Images are stable now 2. md5 is different - the pattern image from sensor+359 is darker than from just the sensor.

MD5 = 60119f4aea02d4624aad045221b4ede0

2008/09/19

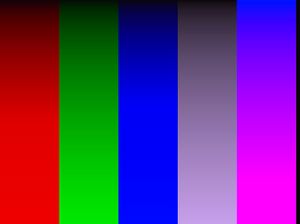

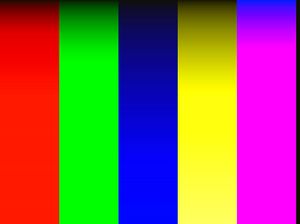

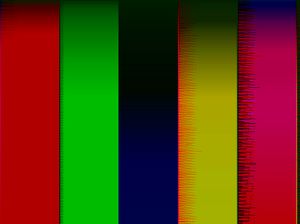

"353+359+2 sensors in ch0 and ch1"

a)

x359.bit:

- data from channel 0 after resync-ing to internal sclk0 goes to output which is synchronous to pclk at 353. Clock tree:

353 -> pclk-> 359's DCM -> sclk0

- other functionality is cut

- experimented with different cables and, sensors

I get good images, sometimes not - looks like depends on the boot. This happens after the power off and the cable from 359 to 353 is a bit deformed, then power on.

Images do not change if the cable is deformed during camera work.

Bad images are unstable and can be of different color, the test pattern is broken, but stable.

Conclusion: Misconfiguration?

| Good | Bad | |

| Test patterns | Etalon (353+sensor) | |

b)

x359.bit:

- data from channels 0 and 1 after resync-ing to internal sclk0 is multiplexed to output which is synchronous to pclk at 353. Clock tree:

353 -> pclk-> 359's DCM -> sclk0

- other functionality is cut

- experimented with different cables and, sensors

All images are broken.

2008/06/09

1. 1 direct + 2 buffered images - done (added 5th cnannel to mcontr - simulated and tested as well). Trying to get difference between frames.

2008/04/25

1. make so that it will take less steps to get the frame from the sensor.

2008/04/22

1. Wrote a script for initializing all the sensors (they needed to set image frame size to 2596x1940 for the compressor to work properly) - sensors_init.php. It just copies parameters from sensor

2. Buffering one frame in DDR and switching between two channels (frame by frame, one buffered, one direct). But this needs to be tested more properly because there's a two black pixel line on the left side - that means Hact is latched two tacts earlier than data.

2008/04/13

1. ch1 - written/read from DDR, ch2 - just comes through.

Simulator output: ch2...ch1-ch2-ch1-ch2

Board output : i can see images changing, but when the compressor is turned on - ch1-ch1-ch1... Does the compressor drop frames (i tried to add a delay (still experimenting))?

2008/04/09

1. "Somehow the last row address I can reach is 0x7ff. Trying simulation".

It's ok now - I was uncarefully modified 'descrproc' module.

2. Test frame is in DDR.

2008/04/08

1. Somehow the last row address I can reach is 0x7ff. Trying simulation.

2008/04/05

1. With a couple of counters removed the memory test eventually ran fine @96MHz (again with bit0 missing). Need to put constraints to that path.

2008/04/04

1. Vact&Hact based on counters - test counter work - do not work

2. Make a memory test, through channel 3 have the ability to read all the DDR - Done, bit0 is not changing. Here's an example (other bits were checked @48MHz and they are ok).

Write DDR Sent array to Row 0x00000003 00030000 00030001 00030002 00030003 00030010 00030011 00030012 00030013 00030020 00030021 00030022 00030023 00030030 00030031 00030032 00030033 Read DDR Acquired data from row 0x00000003 00020000 00020000 00020002 00020002 00020010 00020010 00020012 00020012 00020020 00020020 00020022 00020022 00020030 00020030 00020032 00020032

3. Run a little (for 1 page) memory test @96MHz. This is before phase shift adjust...

Write DDR Sent array to Row 0x00000003 00030000 00030001 00030002 00030003 00030004 00030005 00030006 00030007 00030008 00030009 0003000a 0003000b 0003000c 0003000d 0003000e 0003000f 00030010 00030011 00030012 00030013 00030014 00030015 00030016 00030017 00030018 00030019 0003001a 0003001b 0003001c 0003001d 0003001e 0003001f 00030020 00030021 00030022 00030023 00030024 00030025 00030026 00030027 00030028 00030029 0003002a 0003002b 0003002c 0003002d 0003002e 0003002f 00030030 00030031 00030032 00030033 00030034 00030035 00030036 00030037 00030038 00030039 0003003a 0003003b 0003003c 0003003d 0003003e 0003003f 00030040 00030041 00030042 00030043 00030044 00030045 00030046 00030047 00030048 00030049 0003004a 0003004b 0003004c 0003004d 0003004e 0003004f 00030050 00030051 00030052 00030053 00030054 00030055 00030056 00030057 00030058 00030059 0003005a 0003005b 0003005c 0003005d 0003005e 0003005f 00030060 00030061 00030062 00030063 00030064 00030065 00030066 00030067 00030068 00030069 0003006a 0003006b 0003006c 0003006d 0003006e 0003006f 00030070 00030071 00030072 00030073 00030074 00030075 00030076 00030077 00030078 00030079 0003007a 0003007b 0003007c 0003007d 0003007e 0003007f 00030080 00030081 00030082 00030083 00030084 00030085 00030086 00030087 00030088 00030089 0003008a 0003008b 0003008c 0003008d 0003008e 0003008f 00030090 00030091 00030092 00030093 00030094 00030095 00030096 00030097 00030098 00030099 0003009a 0003009b 0003009c 0003009d 0003009e 0003009f 000300a0 000300a1 000300a2 000300a3 000300a4 000300a5 000300a6 000300a7 000300a8 000300a9 000300aa 000300ab 000300ac 000300ad 000300ae 000300af 000300b0 000300b1 000300b2 000300b3 000300b4 000300b5 000300b6 000300b7 000300b8 000300b9 000300ba 000300bb 000300bc 000300bd 000300be 000300bf 000300c0 000300c1 000300c2 000300c3 000300c4 000300c5 000300c6 000300c7 000300c8 000300c9 000300ca 000300cb 000300cc 000300cd 000300ce 000300cf 000300d0 000300d1 000300d2 000300d3 000300d4 000300d5 000300d6 000300d7 000300d8 000300d9 000300da 000300db 000300dc 000300dd 000300de 000300df 000300e0 000300e1 000300e2 000300e3 000300e4 000300e5 000300e6 000300e7 000300e8 000300e9 000300ea 000300eb 000300ec 000300ed 000300ee 000300ef 000300f0 000300f1 000300f2 000300f3 000300f4 000300f5 000300f6 000300f7 000300f8 000300f9 000300fa 000300fb 000300fc 000300fd 000300fe 000300ff 00030100 00030101 00030102 00030103 00030104 00030105 00030106 00030107 00030108 00030109 0003010a 0003010b 0003010c 0003010d 0003010e 0003010f 00030110 00030111 00030112 00030113 00030114 00030115 00030116 00030117 00030118 00030119 0003011a 0003011b 0003011c 0003011d 0003011e 0003011f 00030120 00030121 00030122 00030123 00030124 00030125 00030126 00030127 00030128 00030129 0003012a 0003012b 0003012c 0003012d 0003012e 0003012f 00030130 00030131 00030132 00030133 00030134 00030135 00030136 00030137 00030138 00030139 0003013a 0003013b 0003013c 0003013d 0003013e 0003013f 00030140 00030141 00030142 00030143 00030144 00030145 00030146 00030147 00030148 00030149 0003014a 0003014b 0003014c 0003014d 0003014e 0003014f 00030150 00030151 00030152 00030153 00030154 00030155 00030156 00030157 00030158 00030159 0003015a 0003015b 0003015c 0003015d 0003015e 0003015f 00030160 00030161 00030162 00030163 00030164 00030165 00030166 00030167 00030168 00030169 0003016a 0003016b 0003016c 0003016d 0003016e 0003016f 00030170 00030171 00030172 00030173 00030174 00030175 00030176 00030177 00030178 00030179 0003017a 0003017b 0003017c 0003017d 0003017e 0003017f 00030180 00030181 00030182 00030183 00030184 00030185 00030186 00030187 00030188 00030189 0003018a 0003018b 0003018c 0003018d 0003018e 0003018f 00030190 00030191 00030192 00030193 00030194 00030195 00030196 00030197 00030198 00030199 0003019a 0003019b 0003019c 0003019d 0003019e 0003019f 000301a0 000301a1 000301a2 000301a3 000301a4 000301a5 000301a6 000301a7 000301a8 000301a9 000301aa 000301ab 000301ac 000301ad 000301ae 000301af 000301b0 000301b1 000301b2 000301b3 000301b4 000301b5 000301b6 000301b7 000301b8 000301b9 000301ba 000301bb 000301bc 000301bd 000301be 000301bf 000301c0 000301c1 000301c2 000301c3 000301c4 000301c5 000301c6 000301c7 000301c8 000301c9 000301ca 000301cb 000301cc 000301cd 000301ce 000301cf 000301d0 000301d1 000301d2 000301d3 000301d4 000301d5 000301d6 000301d7 000301d8 000301d9 000301da 000301db 000301dc 000301dd 000301de 000301df 000301e0 000301e1 000301e2 000301e3 000301e4 000301e5 000301e6 000301e7 000301e8 000301e9 000301ea 000301eb 000301ec 000301ed 000301ee 000301ef 000301f0 000301f1 000301f2 000301f3 000301f4 000301f5 000301f6 000301f7 000301f8 000301f9 000301fa 000301fb 000301fc 000301fd 000301fe 000301ff Read DDR Acquired data from Row 0x00000003 00020000 00020000 00020002 00020002 00020004 00020008 0002000a 0002000a 0002000c 0002000e 00020010 00020010 00020012 00020012 00020014 00020014 00020016 00020018 0002001a 0002001a 0002001c 0002001c 0002001e 0002001e 00020020 00020020 00020022 00020022 00020024 00000000 00000000 00020024 00020026 00020026 00020028 00020028 0002002a 00020050 00020052 00020054 00020056 0002004a 0002004c 00020056 00020058 00020052 00020054 00020058 0002005a 0002005a 0002005c 0002005c 0002005e 0002005e 00020060 00020070 00020072 00020072 00020074 00020074 00020076 0002006e 00020070 00020076 00020078 0002007a 0002007c 0002007c 0002007e 00020088 0002008a 00020080 00020082 00020082 00020084 00020084 00020086 0002008a 0002008c 0002008c 0002008e 0002008e 00020090 00020090 00020092 00000000 00000000 000200a0 000200a2 000200a4 000200a6 000200a6 000200a8 0002009e 000200a0 000200a8 000200aa 000200ae 000200b0 000200b0 000200b2 00000000 00000000 000200b2 000200b4 000200b8 000200ba 000200ba 000200bc 00000000 00000000 000200bc 000200be 000200c0 000200c2 000200c2 000200c4 000200c4 000200c6 000200c6 000200c8 000200ca 000200cc 000200cc 000200ce 000200ce 000200d0 000200d0 000200d2 000200d2 000200d4 000200d4 000200d6 000200d6 000200d8 000200d8 000200da 000200dc 000200de 000200de 000200e0 000200e0 000200e2 000200e2 000200e4 000200e4 000200e6 000200e6 000200e8 00000000 00000000 000200e8 000200ea 000200ee 000200f0 000200f0 000200f2 000200f2 000200f4 000200f4 000200f6 00020100 00020102 00020102 00020104 00000000 00000000 00020104 00020106 00020108 0002010a 0002010a 0002010c 00000000 00000000 0002010c 0002010e 0002010e 00020110 00020110 00020112 00020138 0002013a 0002013a 0002013c 00020142 00020144 00020144 00020146 00020136 00020138 00020146 00020148 00020148 0002014a 0002014a 0002014c 0002014c 0002014e 0002014e 00020150 00020152 00020154 00020154 00020156 00020156 00020158 00020158 0002015a 0002015c 0002015e 0002015e 00020160 00020160 00020162 00020162 00020164 00000000 00000000 00020164 00020166 00020166 00020168 00020168 0002016a 0002016a 0002016c 0002016c 0002016e 0002016e 00020170 00020172 00020174 00020176 00020178 00020178 0002017a 0002017a 0002017c 0002017c 0002017e 00000000 00000000 0002017e 00020180 00000000 00000000 00020180 00020182 00020182 00020184 00020184 00020186 00020186 00020188 00020188 0002018a 00000000 00000000 0002018a 0002018c 0002018e 00020190 00020190 00020192 00020194 00020196 00020196 00020198 00000000 00000000 00020198 0002019a 000201a0 000201a2 000201a2 000201a4 000201c4 000201c6 000201ce 000201d0 000201d0 000201d2 000201d2 000201d4 000201cc 000201ce 000201d4 000201d6 000201d6 000201d8 000201d8 000201da 000201da 000201dc 00000000 00000000 00000000 00000000 00000000 00000000 000201dc 000201de 000201de 000201e0 000201e0 000201e2 000201e2 000201e4 000201fa 000201fc 000201fc 000201fe 000201fe 000201f6 000201f6 000201f8 000201f8 000201fa 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

2008/03/25

1. It's not 10359A yet. 2. There are problems with storing the whole image in the DDR and reading it back. Sync signals were lost. The simulation is ok, but there are too small images. It could be:

a. Incorrect address range written to mcontr registers?! - save the last row address (for 1620x1200, it's near to (2^21)/(2^10 - number of columns in a row)= 2^11 = 0x8000; b. ...

2008/03/20

1. @96MHz, data from sensor replaced by 8 bit counter - there are vertical lines - that means one of the bits is late. Add a phase adjust to the 1st DCM.

2. Apply low drive strength to all the pins interface 353.

This removed vertical lines from section 1.

3. DDR

MaxFrame = (2592x1936)x16 ~ (2^12 x 2^11)x16 = (2^23)x16 = 8M16 = 1 bank of MT46V32M16BN-5B

2008/03/19

1. Initialize/Write/Read DDR @96MHz

It's ok.

2008/03/18

1. make i2c work @96MHz

There's a suspicion it works unstable, so TODO is: a. read an internal counter b. write/read BRAM - done

All's fine. Next Step - Initialize/Write/Read DDR @96MHz. This was unstable because of the need to adjust phase.

2. make the image look like as if data doesn't go through DDR. There're small differences.

All's good Reg Address: 0x0835 Data: bits[4:0]=00001 - channel1 -> DDR -> 359 -> 353 bits[4:0]=00010 - channel2 -> DDR -> 359 -> 353 bits[4:0]=00100 - channel3 -> DDR -> 359 -> 353 bits[4:0]=01001 - counter (accompanied with syncs from sensor1) -> DDR -> 359 -> 353 bits[4]=1 - counter (accompanied with syncs from sensor1) -> 353

2008/03/17

1. Put all FFs to negedge.And verify it. - done

2. Make i2c channels switching work fine - it's ok? but ->

3. i2c first work @96MHz

2008/03/13

TODO:

1. Mistakes during reads?! Check read and write addresses.

!!!! FORGOT TO INITIALIZE CHANNEL 2 !!!!

This chain works fine now:

"sensor -> channel's 0 buffer -> DDR -> channel's 2 line buffer -> to 353"

2008/03/12

1. DDR channel 3 has no problems @48MHz

2. DCM stops working after first try to get the image. It needs to be reseted.

(Address:0x810, Data:0x00000001) (Address:0x810, Data:0x00000000)

3. Simulation model works fine: the stream from "the 3rd" sensor is written line by line to DDR and is read back (line by line as well).

4. The board doesn't work properly (behaviour is different from the simulation model's ).

a. data written to buf0 is ok b. data read from buf2 is not.

2008/02/20

1. I2c check

a. It doesn't work when assemled with mcontr and 2 DCMs. b. Started from the beginning. Works. c. Checked i2c four read with 1 start. Works fine. d. Adding DCMs.

2. Check BRAM read/write. All's fine

3. Check DDR read/write. Some problems. not solved All's fine now

4. Three different boards operate identically: BRAM - ok, DDR - not

a. not marked 359

acquired data is 0x05020306

acquired data is 0x05060706

acquired data is 0x090a0b16

acquired data is 0x0d0e1f16

acquired data is 0x11121316

acquired data is 0x15161716

acquired data is 0x191a1b06

acquired data is 0x1d1e0f26

acquired data is 0x21222326

acquired data is 0x25262726

acquired data is 0x292a2b36

acquired data is 0x2d2e3f36

acquired data is 0x31323336

acquired data is 0x35363736

acquired data is 0x393a3b26

acquired data is 0x3d3e2f46

b. yellow circle marked 359

acquired data is 0x01020306

acquired data is 0x05060706

acquired data is 0x090a0b16

acquired data is 0x0d0e1f16

acquired data is 0x11121316

acquired data is 0x15161716

acquired data is 0x191a1b06

acquired data is 0x1d1e0f26

acquired data is 0x21222326

acquired data is 0x25262726

acquired data is 0x292a2b36

acquired data is 0x2d2e3f36

acquired data is 0x31323336

acquired data is 0x35363736

acquired data is 0x393a3b26

acquired data is 0x3d3e2f46

Channel 3 (test channel) now works fine. And DDR is ok now.

2008/02/20. Understanding how 353's mcontr works

02/28/08: 15:04 for mode=0 ( 8 - burst length)

TileX - number of (32x8) blocks Seq_par(or Param) - the last write block length - (Seq_par)x8 TileY - number of TileX All this starts from StartAddress

2008/02/14

1. Channel 3 simulation:

- DDR initialization through i2c - done.

- write to DDR - done.

- read from DDR - done.

2. PHASE_SHIFT in DCM is not available currently, because the model had bad constructs, but SDCLK(SDNCLK) can be controlled by "phsel".

For correct writing/reading from DDR in model set phsel="01" (register=0x1008, value=0x00000004).